# ACS245MS

20 PIN CERAMIC DUAL-IN-LINE, MIL-STD-1835 **DESIGNATOR CDIP2-T20. LEAD FINISH C**

TOP VIEW

20 PIN CERAMIC FLATPACK, MIL-STD-1835 **DESIGNATOR CDFP4-F20, LEAD FINISH C**

TOP VIEW

20 -)/-

19

18

17

16

15

14

13

12 -77

11

⊐≿

22

72

<u> 77</u>

って

ンと

22

77

<u>д</u> В0

¬ B1

B2 ר

¬ B3

⊐ B4

п В5

п В6

- B7

20 VCC

19 OE

18 B0

17 B1

16 B2

15 B3

14 B4

13 B5

12 B6

11 B7

## **Radiation Hardened Octal Non-Inverting Bidirectional Bus Transceiver**

DIR 1 A0 2

A1 3

A2 4

A4 6

A5 7

A6 8

A7 9

1

2

3

4

5

6

7

8

9

10

GND 10

**?**>

??

->>

22

77

ッン

22

77

22

А0 г

A1 r

A2 r

А3 г

А4 г

А5 г

A6 r

А7 г

GND -

5 A3

**Pinouts**

January 1996

#### Features

- Devices QML Qualified in Accordance with MIL-PRF-38535

- · Detailed Electrical and Screening Requirements are Contained in SMD# 5962-96707 and Intersil' QM Plan

- 1.25 Micron Radiation Hardened SOS CMOS

- Single Event Upset (SEU) Immunity: <1 x 10<sup>-10</sup> Errors/Bit/Day (Typ)

- Latch-Up Free Under Any Conditions

- Military Temperature Range .....-55°C to +125°C

- Significant Power Reduction Compared to ALSTTL Logic

- DC Operating Voltage Range ...... 4.5V to 5.5V

- Input Logic Levels

- VIL = 30% of VCC Max

- VIH = 70% of VCC Min

- Input Current ≤ 1µA at VOL, VOH

- Fast Propagation Delay ..... 15ns (Max), 10ns (Typ)

#### Description

The Intersil ACS245MS is a Radiation Hardened octal non-inverting bidirectional bus transceiver intended for two-way asynchronous communication between data busses.

The ACS245MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of radiation hardened. high-speed, CMOS/SOS Logic Family.

The ACS245MS is supplied in a 20 lead Ceramic Flatpack (K suffix) or a Dual-In-Line Ceramic Package (D suffix).

# **Ordering Information**

| PART NUMBER     | TEMPERATURE RANGE | SCREENING LEVEL       | PACKAGE                  |

|-----------------|-------------------|-----------------------|--------------------------|

| 5962F9670701VRC | -55°C to +125°C   | MIL-PRF-38535 Class V | 20 Lead SBDIP            |

| 5962F9670701VXC | -55°C to +125°C   | MIL-PRF-38535 Class V | 20 Lead Ceramic Flatpack |

| ACS245D/Sample  | 25°C              | Sample                | 20 Lead SBDIP            |

| ACS245K/Sample  | 25°C              | Sample                | 20 Lead Ceramic Flatpack |

| ACS245HMSR      | 25°C              | Die                   | Die                      |

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

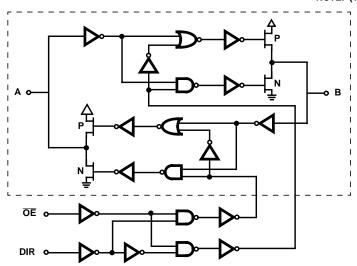

#### **Functional Diagram**

NOTE: (1 of 8)

#### TRUTH TABLE

| INP |     |                 |

|-----|-----|-----------------|

| ŌĒ  | DIR | OPERATION       |

| L   | L   | B Data to A Bus |

| L   | Н   | A Data to B Bus |

| Н   | Х   | Isolation       |

NOTE:

H = High Voltage Level, L = Low Voltage Level, X = Immaterial

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

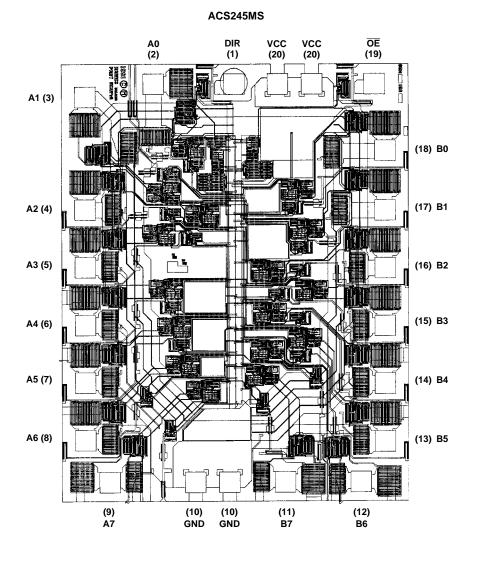

#### **Die Characteristics**

#### DIE DIMENSIONS:

96 mils x 117 mils 2.44mm x 2.97mm

#### **METALLIZATION:**

Type: AlSi Metal 1 Thickness: 7.125kÅ ±1.125kÅ Metal 2 Thickness: 9kÅ ±1kÅ

#### **GLASSIVATION:**

Type: SiO<sub>2</sub> Thickness: 8kÅ ±1kÅ

### WORST CASE CURRENT DENSITY:

$< 2.0 \text{ x} 10^{5} \text{A/cm}^{2}$

#### BOND PAD SIZE:

110μm x 110μm 4.4 mils x 4.4 mils

#### Metallization Mask Layout

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.